|

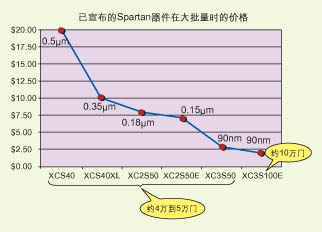

Figure 1: Shows the drop in unit cost for Spartan devices as they roll out different versions of the series. |

The first FPGAs for low-cost portable system applications appeared on the market in the late 1990s. Until then, this market has given way to standard fixed-function devices. At the beginning, FPGAs are usually not the lowest cost solution for such low-cost applications. However, due to its ability to quickly and easily integrate a variety of discrete logic devices, occupying less board space compared to alternatives, and in most cases, saving power, FPGAs soon began to enter into many consumption and Industrial market.

However, as the programmable device is changed from core-limited to pad-limited, the cost formula begins to tilt in favor of the FPGA. Lead limits occur when the die size is entirely determined by the number of I/O pins required rather than by the number of cores. When this happens, the programmability of the wiring overhead will not have much impact on the die size, and thus will not have much impact on the device cost.

It has been a while since wire-limiting has occurred in many standard devices such as ASSPs and ASICs. When the process size is less than 0.5μ, the lead limit problem is encountered for the first time on some smaller FPGA devices.

Today, low-cost FPGAs are leading the process curve with a leading architecture based on 90nm process technology. Stable advances along the process curve, coupled with higher and higher yields on larger wafers, have significantly reduced the cost of FPGAs. According to our calculations, the cost per 1000 logic cells (a standard measure of logic capacity in programmable devices) in low-cost FPGAs has dropped 30-fold since 1998.

The reduced device cost, coupled with the inherent appeal of programmability, means that many system designers will seriously evaluate the FPGA solution versus the fixed-function discrete device solution when making design decisions. At the same time as the cost continues to decline, FPGAs are now replacing various separation logic and other standard products in terms of cost and design ease of use, footprint, and power consumption.

The latest generation of low-cost FPGA device families also includes platform features: support for embedded 8-bit and 32-bit processors, embedded multipliers that provide high-speed DSP capabilities, built-in support for differential signaling, precision system clock resources, etc. Wait. Utilizing these features allows for greater system integration, providing system designers with potential system cost and power savings.

This article details some of the trends in low-cost FPGA devices and presents a system design example that illustrates the logic integration implemented in a low-cost FPGA that saves BOM costs, making design easier and better power characteristics.

|

Figure 2: Spartan Series Low Cost FPGA Unit Cost Reduction |

Low-cost FPGA trends

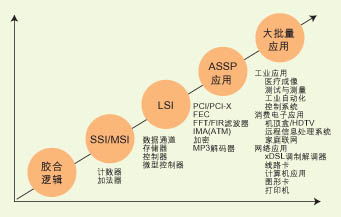

Low-cost FPGAs were originally introduced to provide basic programmable logic structure functionality (stripped all advanced functionality) at a lower cost. The purpose is to use the price elasticity of the existing market to cut into the new high-volume market. At the beginning, low-cost FPGAs are very similar to their corresponding high-end FPGA series in both architecture and process.

When this product category began to be accepted by the market, low-cost FPGAs have developed their own unique architecture and feature set. The latest low-cost FPGAs even use the most advanced 90nm process technology to provide the lowest unit cost. These FPGA families have integrated platform features that allow the integration of complex DSPs, memory control, complex clocking, and processing functions at the lowest cost.

The low price points offered by these new FPGA families can be measured using the unit cost of the device and the cost of a single implementation.

The cost of a single implementation function assumes device unit cost and also assumes that the designer can use most of the remaining device logic to implement system functionality. Regardless of whether this assumption holds, the functional cost is an important indicator when considering the use of FPGAs for core data processing functions in price-sensitive applications.

Xilinx's latest low-cost FPGA family (Spartan-3E series) can implement microprocessors, microcontrollers and digital signal processing functions at a standard price, including a 32-bit MicroBlaze embedded processor with an actual cost of $0.48. An 8-bit PicoBlaze embedded processor that actually costs less than $0.10, and a DSP that is less than $1/GMAC/s.

System architects typically implement glue and interconnect logic in an FPGA before adding peripheral processors and/or DSP processing within the same FPGA fabric. We began to see that the combination of FPGAs and main system controllers/DSPs is increasingly used in data processing.

Today, these systems are only a small part of the low-cost systems that have been applied. However, the price of FPGAs is getting lower and lower, especially with the surge in production using 90-nm processing technology and companies are starting to launch 65-nm products. At the same time, system architects who are more familiar with the platform features of FPGAs will also be able to better utilize these structures to integrate more features.

These two trends ensure that we will see that, as system makers compete more quickly than ever before for a variety of products, and as the cost of low-cost FPGA product lines is lower and more functional, standard programmable devices are Applications in low-cost systems will be further improved.

|

Figure 3: Aster Handheld Tester developed using Spartan FPGA |

System Design Example: Aster Handheld Cable Tester

The ASTER handheld cable tester is used to quickly test copper cables to detect internal short circuits. With the proper adapter, the same system can also be used for wire breakage inspection. The system can identify any diode connected between pins and give a report. The hand-held cable tester also has a parallel port for printing test results through a portable printer.

Performing a quick disconnect inspection of the cable in the field environment requires the use of a portable battery-operated handheld tester. The system works like the expensive top bench cable tester, but it needs to put the logic into a smaller form factor. Traditionally, separate designs will be implemented using separate logic devices. Preliminary estimates show that approximately 70 fixed-function split logic devices need to be used. Each device is a 20-pin package.

This design can not meet the requirements of the mold shell, it can not meet the system power and cost requirements. At the same time, designing with separate devices is also more laborious and inflexible—if the design requirements change in the final implementation phase, a thorough rearrangement of the board may be required.

The second option for implementing this system is to use an FPGA. Using an easy-to-route 208-pin PQFP package with the smallest Spartan FPGA chip and an 8-bit microcontroller (for display and printer functions), the system can be designed on a very flexible and programmable platform. This design method not only saves BOM cost, but also reduces the total power consumption requirement of the system by achieving high integration, so that the handheld cable tester can run continuously for about 5 hours under a single 9V battery power supply.

Using some of the highly efficient synthesis techniques recommended by the Xilinx design software, the entire logic uses only 30% of the available space in the FPGA chip, providing sufficient device space to accommodate design upgrades and requirement changes. The best thing is that its easy-to-complete design features and the ability to change designs in real-time make it possible for engineers to complete the design within eight weeks after the end customer submits the system design specification.

Next version

The next version of the cable tester will be designed for lower cost, smaller form factor, and better power characteristics. To meet these more demanding system specifications requires the use of low-cost FPGAs with more integrated platform features. Xilinx's new Spartan-3L family offers the same low cost and 30% reduction in static power consumption, while providing embedded processing capabilities to implement an 8-bit or 32-bit process using a small portion of the FPGA resources Device. The current series of chips in the next version of the cable tester is being evaluated.

Excerpt from: Electronic Engineering Album

Traditional Reflector,Aluminium Street Reflector,Street Lamp Reflector,Safety Lamp Reflector

Yangzhou Huadong Can Illuminations Mould Manufactory Co., Ltd. , https://www.light-reflectors.com