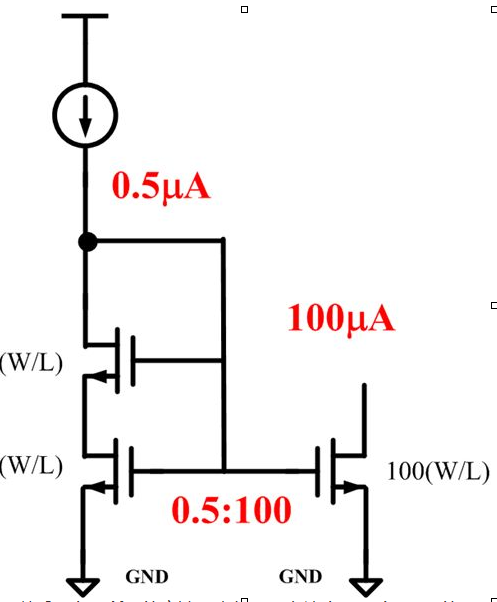

The layout will have a huge impact on the performance of the analog circuit. The matching requirements are very low. The body-effect of nmos can't be underestimated. Even if the current matching is as low as 20%~40%, the matching finally causes a deviation of nearly 50%, which is almost the same. It is 1:600.

When the current matching is not so important, in order to save current and area, you can use the violent raTIo value adopted by the author.

Then I learned a trick, in case the matching requirements are very low, in order to save the area:

You can use the method shown above. Of course, the body-effect of the nmos on the left side can't be underestimated. Let's use it according to your actual situation!

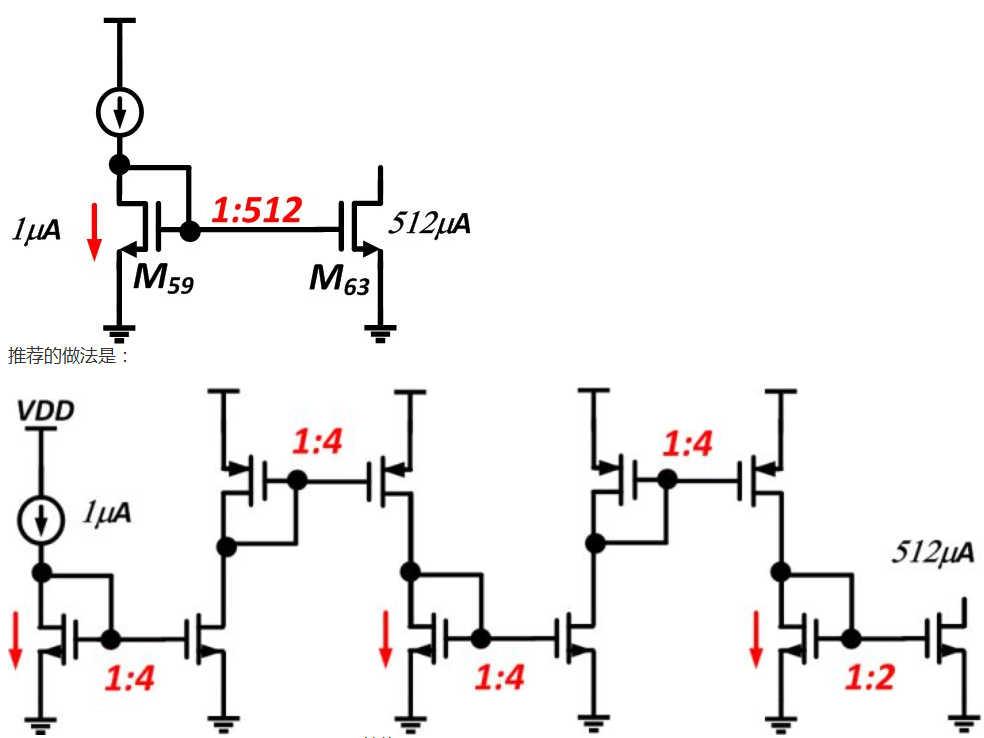

My design has serious flaws, which led to the problem that will be discussed below. Under normal circumstances, current raTIo will probably stay within ten. If this happens:

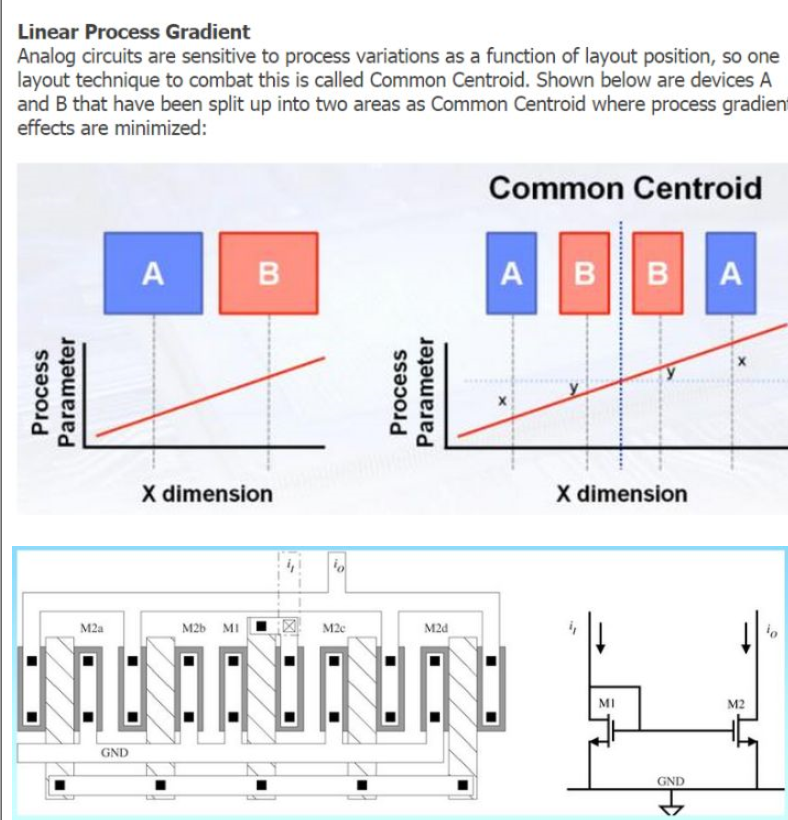

Based on the general classic common-centriod layout structure:

Rather than the approach taken by the author below.

The author was not very worried about his current matching at the time, because he felt that even if it was 20%~40% (1:400 became 1:240 to 1:560), it was tolerable. The result of the post-imitation shows that the matching finally caused a deviation of nearly 50%, which is almost 1:600.

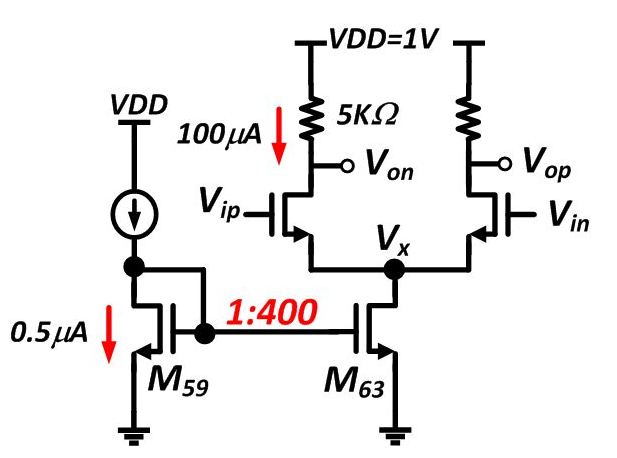

Below is a pre-amplifier for a comparator.

Because the author used to be a low power circuit, it rarely encountered the need to burn a few hundred uA.

So the 200uA pre-amplifier above makes the author depressed.

The W/L raTIo for M59 and M63 is 1:400.

At the beginning of the layout, our layouter asked me, where is this M59?

I didn't have a brain at the time and blurted out: "just pose!"

The words are really good and strong, but the result is a little sad...

After that I took the coupleC and decoupledC to run and imitate. Before jumping well, the DC op of Von and Vop should be 500mV. As a result, I ran a DC and found that it became more than 200 mV... The result is conceivable, and the lower part is all out of the saturaTIon region...

I started thinking that it was a problem when extracting parasitic parameters, so I ran over to find the layouter. Layouter said impossible! In the end, there is no way, I will compare the netlist of the pre-imitation and post-imitation.

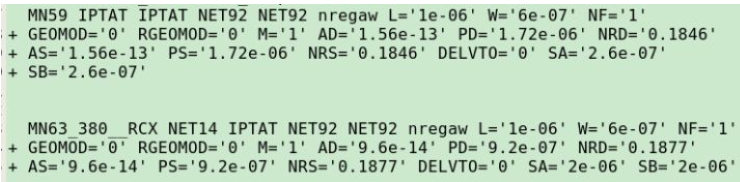

Then the following is the BSIM parameters of M59 and M63 in the post-netlist.

As you can see, for example, the parameter called "AS" is almost twice as fast.

Later, I carefully pondered it. Will it be a layout problem?

Then I went to the layouter to see how the two pipes were placed.

Because I casually said that the M59 is casually placed, so the layouter puts the M59 and M63 together. So this so-called current mirror has no matching at all.

Some layout effects, such as STI, WPE (Well Proximity Effect: Although ion implantation, kinetic ions scatter back out of PR and become embedded in the Si near PR edge, causing VTH shift. The affected distance is ~ 1um. • Small angle II Help, but never avoids WPE.) and so on, have emerged.

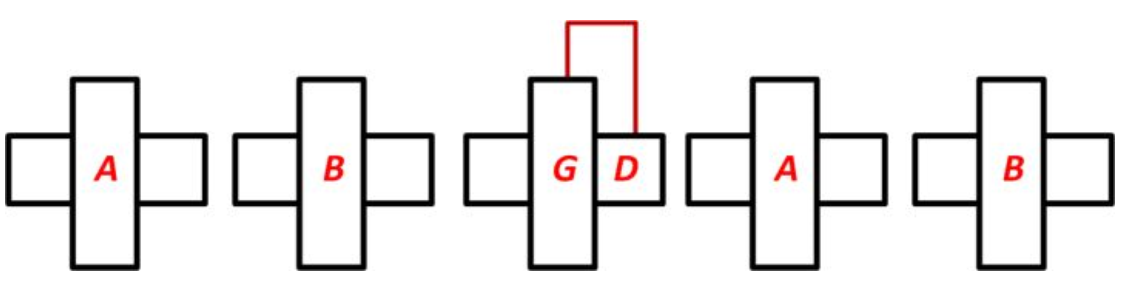

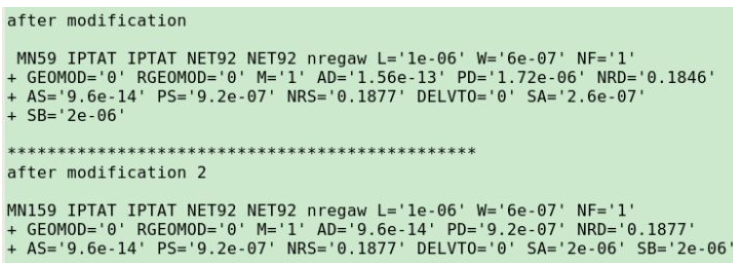

After discovering this problem, I let the layouter insert the M59 into the M63. Does M63 have 400 (multiplier=400)? I changed the M63's m to 399, and the middle one was reserved for M59 (M59 in the netlist below becomes M159)

Support six ports to use at the same time, PD interface projection screen without power, screen projection, transmission, play while charging a draft.

6 in 1 docking station, USB c HUB 6 port type c hub, USB C Hub 6 in 1 with HDMI USB3.0 USB2.0, 6 port multifunction Docking Station

Shenzhen Kingwire Electronics Co., Ltd. , https://www.kingwires.com